SYMPOSIUM POUR L'ÉLECTRONIQUE & LE NUMERIQUE DURABLES

Pôle universitaire d'innovation Grenoble Alpes EN PARTENARIAT AVEC

tech & fest

Large Backer Age

Large Backer A

S

### Table des matières

| 1.Framework d'TA dédié au bâtiment                                                                                                                       | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3. Joint assessment of environmental and social impacts for electronics                                                                                  | 3  |

| 4.Le coût environnemental de l'IA : encourager une recherche efficace par des pénalités computationnelles                                                | 4  |

| 5. Evaluation de solutions limitant les gaz à fort potentiel de réchauffement global pour la gravure par plasma en microélectronique                     | 5  |

| 6.Des indicateurs de fiabilité pour favoriser la réutilisation de smartphones                                                                            | 6  |

| 7. Development and Cooperative Validation of an Eco-Design Methodology for Wet Processes in Semiconductor Manufacturing: An Industrial Consortium App    | •  |

| 8.Identification des possibilités d'économies de wafers utilisés comme témoins ou pour le suivi de la stabilité d'équipements                            | 8  |

| 9.Comment faire perdre les kilogrammes de CO <sub>2</sub> de la microélectronique avant l'été?                                                           | 9  |

| 10.La Twin Transition dans le secteur de la construction                                                                                                 | 10 |

| 11.Extension de la méthode d'Analyse de Cycle de Vie à un environnement de R&D, à partir de l'étude d'un cas d'usage prototype                           | 11 |

| 12.ACV du SiC : de la matière première au convertisseur                                                                                                  | 12 |

| 13.Distillation fédérée dans une infrastructure de Edge computing                                                                                        | 13 |

| 14.Méthodologie pour mesurer la plus-value environnementale des convertisseurs de puissance à composant grand gap (SiC, GaN)                             | 14 |

| 15.Modèle réduit LSTM pour l'optimisation de transistors bipolaires à hétérojonction silicium-germanium                                                  | 15 |

| 16.Appa LCA : un workflow d'intégration de l'analyse de cycle de vie pour l'écoconception des systèmes numériques                                        | 16 |

| 17.Étude et modélisation de l'impact carbone des circuits imprimés                                                                                       | 17 |

| 18.General-Purpose Long-Lasting Computing Platform                                                                                                       | 18 |

| 19.Le numérique durable peut-il être anti-écologique ? Récit d'une manifestation contre l'industrie de la micro-électronique grenobloise                 | 19 |

| 20. Analyse de Cycle de Vie de la fabrication de semiconducteurs: Un guide pour la réduction des impacts environnementaux                                | 20 |

| 21.Beyond the quest for performance in conversion electronics                                                                                            | 21 |

| 22.Modèles d'impact carbone des capteurs d'image CMOS                                                                                                    | 22 |

| 23.Sustainable Electronics: what kind of sustainability? Some examples in the field of microwave devices                                                 | 23 |

| 24.Éco-conception du PCB : comment améliorer son cycle de vie grâce à des bio-matériaux et de nouvelles approches de conception de la carte électronique | 24 |

| 25.Ferroelectric Spin-Orbit devices for ultralow-power computing and AI                                                                                  | 25 |

| 26.Analyse de cycle de vie adapté au logiciel : outillages et recommandations                                                                            | 26 |

| 27.The Reality of Digital                                                                                                                                | 27 |

| 28.AUTONOMOUS DUAL SENSOR USING GAN ON SILICON TECHNOLOGY FOR SUSTANAIBLE IOT                                                                            | 28 |

| 29.Contrôle frugal de robot                                                                                                                              | 29 |

| 30. FABRICATION D'UNE ELECTRONIQUE ECORESPONSABLE EN UTILISANT DU PAPIER ET DES PROCEDES L'ELECTRONIQUE IMPRIMEE                                         | 30 |

| 31.PLATEFORMES IOT POUR L'ENSEIGNEMENT ET LA RECHERCHE SUR L'ELECTRONIQUE FRUGALE ET EFFICIENTE                                                          | 31 |

| 32.SIMPLIFIED CRADLE TO GATE LIFE CYCLE ASSESSMENT OF SIC TRANSISTOR FABRICATION                                                                         | 32 |

| 34.ÉVALUER LES IMPACTS ENVIRONNEMENTAUX ET OPTIMISER LES INNOVATIONS POUR LES RESEAUX RADIO POST-5G                                                      | 33 |

| 35.ECOCYCLEQUEST: SENSIBILISER AUX IMPACTS ENVIRONNEMENTAUX DU NUMERIQUE PAR LE JEU                                                                      | 34 |

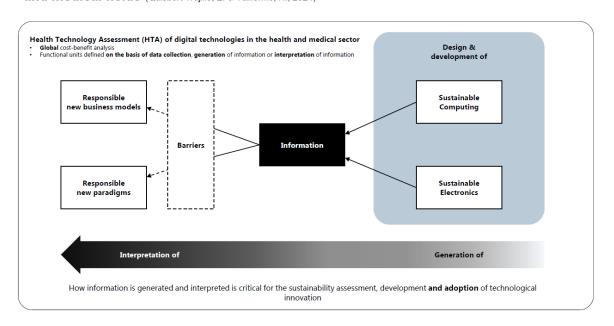

| 36.TOWARDS THE OPERATIONALIZATION OF SUSTAINABLE DIGITAL HEALTH                                                                                          | 35 |

| 37.METHODOLOGIE DE CONCEPTION DE COMPOSANTS ELECTRONIQUES DURABLES                                                                                       | 36 |

| 38.PARAMETRIC LCA BASED ECODESIGN PROCESS FOR ELECTRONICS PRODUCT DEVELOPMENT                                                                            | 37 |

| 39.GREENCHIPS-EDU PROJECT: EDUCATE FOR A SUSTAINABLE TOMORROW                                                                                            | 38 |

| 40.DESIGN OF AN ARITHMETIC LOGIC UNIT (ALU) USING FERROELECTRIC SPIN ORBIT (FESO) DEVICES FOR LOW POWER COMPUTING                                        | 39 |

| 41.L'EVASION NUMERIQUE ET L'ODYSSEE NUMERIQUE : DEUX SUPPORTS DE SENSIBILISATION AUX ENJEUX DU NUMERIQUE RESPONSABLE                                     | 40 |

| 43. Vers une feuille de route de la recherche de la soutenabilite en electronique de puissance                                                           | 41 |

| 44.Enjeux de l'électronique imprimée sur support cellulosique – vers une approche durable                                                                | 42 |

|                                                                                                                                                          | 4  |

Réf: A17154LC

Louis Closson - Auteur presentateur - Université Grenoble Alpes, Grenoble, France

Christophe Cérin - Université Sorbonne Paris Nord, France

Didier Donsez - Adeunis, CROLLES, France

### 1.Framework d'IA dedie au batiment

Le secteur du bâtiment est responsable de près de 40 % de la consommation d'énergie et 33 % des émissions de CO<sub>2</sub>. Cela concerne principalement les bâtiments tertiaires. La mise à niveau des équipements de chauffage, ventilation et climatisation (CVC) poursuit alors deux buts :

- Le premier vise au confort des occupants et cible la température, l'humidité et la qualité de l'air. Des normes de surveillances, contractualisées, imposent la remontée régulièrement d'informations. Une juste inquiétude sur la salubrité de l'environnement intérieur est apparue avec la Covid, et l'Internet des Objets (IdO) a démontré une excellente adaptabilité afin de permettre une surveillance accrue qui permet le respect des nouvelles obligations légales.

- Le second but de la mise à niveau des CVC est la réduction de consommation d'énergie (voir décret tertiaire), devenue critique avec les tensions grandissantes du marché de l'électricité. Cette contrainte, bien que primordiale, entre généralement en contradiction avec la nécessité de confort des occupants du bâtiment, qui sont bien souvent différents des organisations facturées (les gestionnaires du bâtiment).

Une conséquence directe de cette complexification du bâtiment est donc le coût du maintien des équipements, et l'expertise requise, qui délaissent l'optimisation du pilotage des bâtiments par manque de temps ou de main d'oeuvre qualifiée, malgré les efforts légaux déployés (décret BACS).

L'écosystème IdO permet cependant l'émergence rapide de l'intelligence artificielle, par la richesse et la pertinence des données récupérées, et laisse envisager une nouvelle transition imminente du secteur du bâtiment, qui passe du contrôle par règles au contrôle prédictif. L'intelligence artificielle promet une adaptabilité peu effective pour le moment par les modèle auto-adaptatifs.

La mise en place de solution d'IA durables requiert alors des solutions du secteur MLops, avec un suivi et maintien des données utilisées, afin de promettre des IA robustes qui répondent aux enjeux de fiabilité. Il s'agira d'un procédé itératif d'amélioration continu, reposant à la fois sur des statistiques de gestion du bâtiment, et sur le partage des modèles créés. L'apprentissage fédéré de modèles de gestion du bâtiment, provenant de différentes sources, requiert le concourt des acteurs du bâtiment, de l'IoD et de l'IA et promet ainsi des solutions innovantes.

SANDIONIGI Chiara - Auteur presentateur - CEA, Grenoble, France

## 3.JOINT ASSESSMENT OF ENVIRONMENTAL AND SOCIAL IMPACTS FOR ELECTRONICS

The electronics industry is recognized to have a significant impact on the environment both for the production and usage of the devices. Less acknowledged are the social impacts related to this industry, despite the associated harmful effects and risks for human beings. Life Cycle Assessment (LCA) is a recognized method to assess environmental and social impacts, and to identify the hotspots in the life cycle of a product. While environmental and social LCAs share the same phases for the analysis, their objectives and target impacts are substantially different. Hence, the two assessments are usually carried out separately. Besides being time consuming, this approach leads to consider the environmental and social pillars of sustainability as two separate dimensions. Consequently, eco-design and social design continue to be distinguished strategies without common analysis, possibly leading to different decisions based on the same data.

Our work combines for the first time environmental and social LCA in a single methodology to allow a joint evaluation of environmental and social impacts. The focus is on the sharing of analyses and data with the final objective of defining an eco-social LCA. We highlight the features common to the two assessments, the stages only partially shareable, and the parts with a scope exclusively environmental or social. We also consider the choice of using separate databases for environmental and social data, or a common database. The methodology has been applied to an Integrated Circuit, a case study where the social assessment constitutes an almost unexplored domain. This allowed validating the common analyses and data between the two assessments, while the ecosocial LCA of the circuit still constitutes a work in progress because of the access to reliable and specific data and the induced modelling challenges.

The work constitutes a first step towards eco-social design applied to the domain of electronics. One of the main benefits of the proposed eco-social LCA is to facilitate the social assessment by sharing data and analyses with the environmental counterpart. This will possibly allow fastening the development of the social pillar of sustainability, as already happened to the environmental one in the last years.

GHOLIPOUR PICHA Sayeh - Auteur presentateur - Grenoble INP CNRS, Saint-Martin-d'Hères, France

## 4.LE COUT ENVIRONNEMENTAL DE L'IA: ENCOURAGER UNE RECHERCHE EFFICACE PAR DES PENALITES COMPUTATIONNELLES

Dans le domaine de la recherche, en particulier en intelligence artificielle, des avancées majeures ont été réalisées grâce à l'émergence des mécanismes d'attention et des transformeurs, ouvrant une nouvelle ère d'innovation. Ces percées ont permis aux modèles de capturer des motifs complexes dans les données avec une précision remarquable. Le succès de ces travaux est souvent mesuré par la performance des modèles, entraînant une forte concurrence entre les centres de recherche et les entreprises pour obtenir les meilleurs résultats dans les délais les plus courts.

Pour rester compétitives, les organisations investissent massivement dans des serveurs de haute performance et développent des modèles avec un nombre énorme de paramètres, en exécutant des calculs continus pour maximiser les résultats. Si ces efforts ont conduit à des avancées impressionnantes, ils ont également entraîné une empreinte carbone considérable, soulevant des préoccupations sur la durabilité de ces pratiques.

Pour répondre à cette problématique environnementale, nous proposons d'introduire des pénalités sur l'utilisation excessive des ressources de calcul, proportionnellement à la taille du modèle et aux gains de performance. Souvent, les modèles sont réentraînés pour des améliorations marginales, malgré une empreinte carbone importante. Lorsque les gains sont minimes, la valeur de ces recherches doit être réévaluée. En décourageant ces pratiques inefficaces, la communauté IA pourrait être incitée à prioriser la réduction des émissions de carbone plutôt que la course à l'amélioration marginale. Si la performance d'un modèle ne dépasse pas significativement les références existantes, de nouveaux entraînements devraient être considérés comme inefficaces, sauf si des approches plus durables sont employées.

Cette approche pourrait également affecter la tendance à développer de nouveaux modèles de langage de grande taille, souvent similaires. De nombreux modèles sont développés par des entreprises ayant une empreinte carbone significative, ce qui soulève des questions quant à savoir si ces développements font réellement progresser le domaine ou s'ils sont principalement motivés par des intérêts financiers. L'introduction de pénalités environnementales contribuerait à réorienter l'attention vers des recherches significatives et durables.

Aligner la recherche en IA sur la durabilité encouragerait le développement de modèles plus économes en énergie, tout en promouvant l'innovation avec un moindre impact écologique.

SARRAZIN Aurélien - Auteur presentateur, BOULARD François, BOIXADERAS Christelle, SERVIN Isabelle, CHEVOLLEAU Thierry - CEA-Leti, GRENOBLE, France

# 5.EVALUATION DE SOLUTIONS LIMITANT LES GAZ A FORT POTENTIEL DE RECHAUFFEMENT GLOBAL POUR LA GRAVURE PAR PLASMA EN MICROELECTRONIQUE

L'industrie de la micro-électronique s'est engagée sur la voie de la durabilité avec l'objectif d'atteindre des émissions proches de zéro d'ici 2050. Ces dernières années, des Analyses de Cycle de Vie (ACV) ont été menées pour caractériser l'impact de technologies ou de produits pour des applications du domaine des semi-conducteurs au CEA-Leti et dans d'autres groupes de recherche. Outre les coûts environnementaux générés par l'utilisation de salles blanches pour réaliser les opérations de fabrication, les étapes de gravure par plasma ont été ciblées pour l'impact de leurs rejets sur le réchauffement climatique. En effet, des gaz de gravure à très fort potentiel de réchauffement global (PRG ou GWP en anglais) sont couramment utilisés pour réaliser ces étapes, ils peuvent avoir un impact sur l'atmosphère des milliers de fois supérieurs à celui du CO2. Pour limiter l'impact de ces gaz, des systèmes d'abattement sont implémentés sur les équipements de dernières générations afin de limiter l'émission de ces rejets gazeux dans l'atmosphère. Néanmoins leur efficacité n'a jamais été évaluée dans des conditions réelles de gravure pour des intégrations pertinentes. Ces données d'abattement sont cruciales dans les résultats d'études ACV devant permettre de définir les points critiques et donc les priorités pour rendre les procédés plus vertueux vis-à-vis de l'environnement. Le CEA-Leti s'engage ainsi sur l'évaluation de ces rejets dans des conditions de procédés réelles comme alternative aux données du GIEC qui sont aujourd'hui utilisées dans toutes les ACV.

Après avoir évalué les procédés actuels utilisant des gaz à fort potentiel de réchauffement global, l'étude de solutions plus durables sera envisagée avec des gaz alternatifs existants ou de nouvelles molécules perfluorocarbonées développées par des industriels de la chimie. Ces nouvelles molécules, dont le PRG est proche de zéro, doivent être évaluées sur des intégrations pertinentes afin de répondre aux enjeux techniques (contrôle dimensionnel, vitesse de gravure, etc.), de valider l'absence d'effets rebonds (surconsommation d'énergie par exemple) mais également qu'après gravure et abattement des sous-produits avec un PRG élevé ne soient pas favorisés.

BRUSSELMANS Nicolas - Auteur presentateur - CEA-Leti - UCLouvain, Louvain-la-Neuve, Belgium, GRENOBLE, France,

FERON Jean-Brieuc - Citronics, Bruxelles, Belgium,

RASKIN Jean-Pierre - UCLouvain, Louvain-la-Neuve, Belgium

## 6.DES INDICATEURS DE FIABILITE POUR FAVORISER LA REUTILISATION DE SMARTPHONES

Pour limiter l'impact environnemental et sociétal de l'électronique, l'économie circulaire et particulièrement l'approche des 3Rs est bien connue : Réduire, Réutiliser, Recycler. Chacun de ces piliers peut se décliner en une multitude de stratégies. Par exemple, la réutilisation peut s'appliquer à une fonction (reconditionnement), un système (réaffectation) ou à ses composants (refabrication / surcyclage). Chacune de ces méthodes nécessite une évaluation approfondie de la fiabilité du dispositif en fin de première vie, afin de fournir un nouveau produit qui correspond à des exigences définies. Cette évaluation est particulièrement difficile puisque deux appareils similaires peuvent avoir été utilisés très différemment durant leur première vie et présenter des taux d'usure variés.

Une solution pour réaliser cette évaluation est de se focaliser sur des indicateurs de fiabilités, des métriques qui peuvent se mesurer 1) macroscopiquement, en limitant les étapes de démontage et les procédés de tests coûteux en ressources, 2) rapidement, pour permettre l'industrialisation et 3) de manière non-destructive, en vue d'une future réutilisation. Le cas des mémoires flash fournit un bon exemple d'indicateur de fiabilité, puisqu'il existe une corrélation entre le temps d'écriture et le taux d'usure d'une mémoire.

Afin de découvrir les indicateurs pertinents et de valider leur capacité à évaluer la fiabilité, une expérience en deux phases est mise en place. Elle s'inscrit dans l'environnement de Citronics, une start-up Bruxelloise qui récupère des smartphones obsolètes à échelle industrielle et les réaffecte en micro-ordinateurs. L'objectif de la première phase est de découvrir les relations entre indicateurs et fiabilité en faisant subir des tests de vie accélérée à une flotte d'appareils. Ces tests destructifs permettent d'extraire les métriques d'intérêt jusqu'à la défaillance totale. Dans un second temps, ces indicateurs sont validés sur les appareils réaffectés par Citronics, en mettant en relation les métriques mesurées et la fiabilité observée sur le terrain. Le smartphone étant un système complet composés de plusieurs sous-systèmes génériques comme le processeur et les mémoires, les indicateurs pertinents pourront être utilisés pour caractériser la fiabilité d'autres appareils électroniques, tels que les ordinateurs ou les serveurs.

Réf: A17132MA

Marine AUDOUIN - Auteur presentateur, VALETTE Audrey - TECHNIC France, Saint Denis, France,

ALLOUTI Nacima, STIGLIANI Mathieu, MEHREZ Zouhir, VANDENBOSSCHE Martin, CHEVOLLEAU Thierry – CEA-Leti, Grenoble, France

DAVIOT Jérôme - TECHNIC France, Saint Denis, France

## 7.DEVELOPMENT AND COOPERATIVE VALIDATION OF AN ECO-DESIGN METHODOLOGY FOR WET PROCESSES IN SEMICONDUCTOR MANUFACTURING: AN INDUSTRIAL CONSORTIUM APPROACH

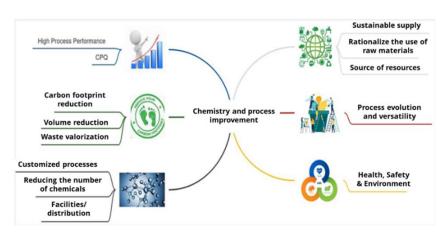

Europe's ambitions for the microelectronics industry aim to increase competitiveness and market share while reducing its environmental impact. To meet these targets, it is necessary to incorporate a more systemic approach when designing new surface preparation solutions. This includes additional criteria such as Health, Safety and Environment (HSE) assessment, raw materials sustainability carbon footprint, consumption per square inch (chemistry, energy), waste management including valorization, in addition to performance and cost considerations.

To accelerate the development and validation of those eco-designed solutions, a consortium has been formed, included TECHNIC, CEA-Leti and an industrial actor under the "CLEAN" project, standing for "Effective Liquid Chemistries for Nanotechnology improvement".

The CLEAN project offers an opportunity to realize almost real-time industrial research and experimental prototypes evaluation from the front-end of line (FEOL) to packaging, from lab scale to representative industrial environment. Through joined development, process performance monitoring, risk assessments, and life cycle analyses, the project aims to demonstrate the feasibility of reducing the impact of surface preparation processes. Indeed, historical wet processes today raise concerns of HSE, energy consumption and sustainability. They therefore need to be replaced. (Figure 1).

The initial results are promising and include the development by TECHNIC of Non-toxic, CMR-free formulations meeting the consortium'products specifications. In particular the replacement of TMAH and hydroxylamine-based solutions (respectively neurotoxic and CMR components) for stripping photoresist resins and selectively removal of post etch residues. All the new processes developed are currently being tested on CEA pilot lines and are at least as effective as historical processes. This decisive step allows the process to be customized before transfer to the end-user.

By adopting this approach, involving a chemical formulator, an RTO and an end-user, all partners intend to minimize the risk of legacy processes replacement, share development/evaluation cost, accelerate the qualification cycle while proposing sustainable and innovative surface preparation processes.

BAILLET Francis - Auteur presentateur - CEA-Leti, Grenoble, France

## 8. IDENTIFICATION DES POSSIBILITES D'ECONOMIES DE WAFERS UTILISES COMME TEMOINS OU POUR LE SUIVI DE LA STABILITE D'EQUIPEMENTS

Le CEA-LETI, institut de recherche technologique de CEA Tech, a pour mission d'innover et de transférer les innovations à l'industrie. Son coeur de métier réside dans les technologies de la microélectronique, de miniaturisation des composants, d'intégration système, et d'architecture de circuits intégrés. Le Département des PlateFormes Technologiques regroupe tous les moyens opérationnels (salle blanche, équipements et procédés) du LETI. La consommation de wafers pour des usages comme témoins ou pour le suivi de la stabilité et la fiabilité des équipements utilisés peut représenter jusqu'à 40 000 wafers / an sur l'ensemble des équipements du DPFT. Cette activité est consommatrice de substrat de Silicium de première qualité et la diminution de cette consommation est importante pour répondre aux enjeux de réduction de l'empreinte environnementale du site.

L'objectif du travail présenté est de rationaliser et optimiser l'utilisation de plaques témoins pour le suivi des équipements (SDE) en mutualisant les substrats au profit de plusieurs ateliers ou procédés. Ce seul suivi d'équipement consomme 25% des 40 000 wafers annuels.

Pour identifier les possibles ré utilisations multiples d'un même wafer, une base de données a été constituée avec de nombreuses propriétés, pour chaque type de témoin, allant du diamètre du wafer à la personne en charge des suivis d'équipement. Cette base seule n'est pas exploitable et nécessite d'y ajouter les relations entre les équipements ou les procédés utilisés. Il a donc été nécessaire d'utiliser une base de données de type « graphe » à même d'intégrer, à la fois un très grand nombre de procédés, un grand nombre de propriétés et de relations entre équipements ou procédés. L'exploitation de la base constituée à ce jour a permis d'identifier 16 produits pouvant être ré utilisés en interne et de nombreuses pistes de rationalisation.

La base constituée (encore partielle) et l'exploitation qui en a été faite, permettent d'espérer une économie de 30% des wafers utilisés annuellement pour ces suivis et témoins. L'intégration de wafers utilisés pour qualifier un équipement après un arrêt pour maintenance permettrait d'augmenter encore le taux de réutilisation des wafers et donc les économies engendrées.

BILLAUD Mathilde - Auteur presentateur - CEA-Leti, Grenoble, France

## 9. COMMENT FAIRE PERDRE LES KILOGRAMMES DE CO<sub>2</sub> DE LA MICROELECTRONIQUE AVANT L'ETE ?

Cette présentation commencera par un court exposé satirique dénonçant les dérives de la soutenabilité en microélectronique pour ensuite énoncer les bonnes pratiques nécessaires à une microélectronique réellement durable. Après 4 années du programme écoinnovation au Leti, nous souhaitons tirer des leçons et donner des recommandations pour la suite. Parmi les enseignements encourageants et stimulants, nous pourrons mentionner la présence quasi inévitable des aspects environnementaux dans les discussions actuelles ainsi que la participation enthousiaste et active du personnel R&D autour de ces sujets. Cependant, nous démontrerons par des exemples concrets et récents de l'actualité des semi-conducteurs, que cette industrie ne prend pas la voie de la frugalité pourtant inévitable pour une réelle compatibilité avec les limites planétaires. Nous proposerons des recommandations aux industriels et chercheur euse s de ce domaine pour accompagner les semi-conducteurs vers un chemin écoresponsable en phase avec les objectifs de la lutte contre le réchauffement climatique.

VERNAY Anne-Lorène - Auteur presentateur, RANVILLE Adélie, GENET Corine, DIELER Clemens Grenoble Ecole de Management, Grenoble, France

### 10.LA TWIN TRANSITION DANS LE SECTEUR DE LA CONSTRUCTION

La transition numérique dans les entreprises a fait l'objet de nombreuses études. La recherche a montré qu'elle peut aider les entreprises à être plus productives ou à innover. Nous nous demandons si l'adoption des technologies numériques peut également aider les entreprises à effectuer une transition vers des émissions nettes de carbone nulles. Pour ce faire, nous menons une étude de cas qualitative auprès d'entreprises du secteur de la construction. A ce stade, nous avons réalisé 20 entretiens avec des représentants de quatre cimentiers, d'un cabinet d'architecture, d'une entreprise de construction et d'un acteur de la rénovation énergétique des bâtiments. Nous étudions comment les entreprises gèrent leur transition vers le net-zéro et analysons si, comment et pourquoi l'adoption des technologies numériques peut les y aider. Nous analysons les changements apportés par les entreprises au niveau du Business Model. En nous basant sur l'archétype du Business Model Durable (BMD) de Bocken et al. (2014), nous analysons les Business Models adoptés par les entreprises et la manière dont elles utilisent les technologies numériques dans ce cadre. Les résultats préliminaires montrent que les principales SBM mises en oeuvre sont : maximiser l'efficacité, créer de la valeur à partir des déchets, substituer des matériaux et encourager la suffisance. Les technologies numériques sont rarement à l'origine de l'adoption de ces SBM.

Nous constatons cependant que les technologies numériques peuvent aider à surmonter des défis spécifiques liés à la mise en oeuvre de certains SBM, par exemple, inclure de nouveaux matériaux (substitution) ou des matériaux d'entrée hétérogènes (provenant de déchets) tout en garantissant la stabilité de la performance du produit.

Nous constatons que les outils numériques sont également utilisés pour suivre les émissions de carbone, les signaler et donner de la visibilité à la proposition de valeur à faible teneur en carbone.

Enfin, nos observations suggèrent que l'adoption de la GAE est limitée par le fait que les acteurs de la chaîne d'approvisionnement ne sont pas en mesure d'accéder aux données requises dans une qualité et un format adéquats, notamment les données relatives à l'empreinte carbone exacte des matériaux.

Réf: A17124TH

HALTER Thibault, Makan - Auteur presentateur, PERALTA Maxime

Univ. Grenoble Alpes, CEA, List, Grenoble, France

# 11. Extension de la methode d'Analyse de Cycle de Vie a un environnement de R&D, a partir de l'etude d'un cas d'usage prototype

Afin de répondre au contexte global de crise environnementale, une réflexion émerge, consistant à inclure la notion d'Analyse de Cycle de Vie (ACV) au plus proche des décisions directrices des projets de recherche.

Systématiser la démarche d'ACV dans le secteur du numérique nécessite d'identifier les points chauds, de définir des hypothèses de modèles robustes permettant de réduire les incertitudes qui leurs sont associées, et de déterminer l'ensemble des conjectures permettant de convertir des données design numérique en impacts environnementaux.

Une première ACV a été menée sur un projet de puce embarquant une Near Memory Computing (NMC), utilisant la technologie C-SRAM[1], et intégrée à une carte test. Les modèles d'Inventaire du Cycle de Vie (ICV) ont été construits sur EIME, en utilisant les bases de données CODDE et Negaoctet, avec la méthode PEF.

En attendant les données de simulation concernant la phase d'utilisation, l'ACV a été conduite du berceau à la porte, en s'appuyant sur un certain nombre d'hypothèses, concernant principalement la taille, le noeud et la provenance des circuits intégrés (IC). Ce modèle, constitué à partir d'une liste de plus de 200 composants, a été challengé en comparant la masse modélisée (202 g) avec celle de l'objet réel de notre étude (237 g), ce qui a induit des hypothèses complémentaires permettant d'éviter une sous-évaluation des impacts.

L'importante contribution des IC et des PCB dans les impacts environnementaux du système prototype étudié appuie sur la nécessité de réduire les incertitudes associées aux hypothèses utilisées.

L'objectif sous-jacent est désormais triple :

Projeter les impacts du prototype sur une version industrialisable.

Contourner les incertitudes (mapping des dimensions des IC par techno de package).

Dresser une listes d'hypothèses complémentaires (ex. détermination d'un BOM générique par cm2 de PCB).

FIGURE : Résultats intermédiaires (en score unique) de l'ACV StorAlge pour la partie Manufacturing

[1] Maha et al.; 2021; "Storage Class Memory with Computing Row Buffer: A Design Space Exploration", ; Design, Automation and Test in Europe Conference (2021)

Réf: A17120EC

CHAUMAT Elise - Auteur presentateur - CEA - Leti, Grenoble, France

### 12.ACV DU SIC: DE LA MATIERE PREMIERE AU CONVERTISSEUR

Global electricity demand keeps surging, driven by emerging economies, the expansion of telecommunication infrastructures, datacentres, and the ongoing electrification for decarbonation purposes. In this context, demand for Power Electronic (PE) systems is rising, making their sustainability a key issue. Indeed, PE systems are made of a wide variety of materials, rare minerals and plastics. Furthermore, manufacturing the electronic components they rely on requires huge amounts of energy, water and chemicals. Finally, PE systems adapt energy between various sources. This energy conversion is characterised by energy losses. Therefore, to ensure PE systems become a solution to environmental issues rather than increasing them, one must minimise their environmental impacts.

Wide Band Gap (WBG) semi-conductor materials such as Gallium Nitride (GaN) and Silicon Carbide (SiC) are forseen to significantly reduce the environmental impacts of PE converters. First, shifting from Silicon (Si) to WBG decreases conduction and switching losses, resulting in greater energy efficiency. Second, the high switching speed of WBG components enables to increase their operating frequencies, and consequently reduce the number of passive components. However, WBG components are more impactful to produce than Si. For instance, manufacturing a bulk SiC wafer leads to 79 times more CO2 emissions than Si wafers [1]. Thus, understanding the environmental impacts of these new components has become essential to understand when WBG are relevant to use, and when they are not. Unfortunately, data concerning the environmental impacts of WBG technologies is scarce. A Life Cycle Analysis (LCA) was carried out on GaN device [2], but none on SiC: the main publications relative to SiC impacts rely merely on energy consumption [3][4].

The European Project Fastlane gathers European actors from the whole value chain of SiC inverters, from SiC powder manufacturing up to PE converters, offering the opportunity to collect data in real industrial settings along the chain. As such, this project ambitions to produce an LCA of SiC at substrate, device, power module and inverter level, for both automotive and stationary applications. This talk will describe the methodology implemented to carry out consistent LCA with such a wide variety of actors.

- [1] Musil F. et al., How Life Cycle Analyses are Influencing Power Electronics Converter Design, PCIM Europe 2023, 09 11 May 2023, Nuremberg, https://doi.org/10.30420/566091368

- [2] Vauche L. et al, Cradle-to-Gate Life Cycle Assessment (LCA) of GaN Power Semiconductor Device, Sustainability 2024, 16, 901. https://doi.org/10.3390/su16020901

- [3] Triana D. et al., A "life cycle thinking" approach to assess differences in the energy use of SiC vs. Si power semiconductors. In Proceedings of the e.nova 2021 Conference "Green Deal, Energy Building Environment", 12 February 2022; p. 10. https://www.iea-4e.org/wpcontent/uploads/publications/2022/01/DiazSchmidtGlaserMakoschitz\_LCThinkingWBG\_For\_PECTA.pdf

- [4] Warren J.A., Energy Impacts of Wide Band Gap Semiconductors in U.S. Light-Duty Electric Vehicle Fleet, Environ. Sci. Technol. 2015, 49, 10294–10302, https://pubs.acs.org/doi/10.1021/acs.est.5b01627

FRESSE Virginie - Auteur presentateur - Université Jean Monnet, Saint Etienne, France,

MARON Cedric- Université Jean Monnet, Saint Etienne, France - Segula Technologies, Villeurbanne, France,

OHAYON Avigael - Segula Technologies, Villeurbanne, France

## 13.DISTILLATION FEDEREE DANS UNE INFRASTRUCTURE DE EDGE COMPUTING

A l'ère des réseaux de neurones de plus en plus gourmands en capacité calculatoire et mémoire, l'intégration de ces modèles dans des composants dits « légers » nécessaires pour répondre aux enjeux de l'IA frugale devient un des principaux challenges. De nombreuses techniques d'optimisation ont vu le jour et permettent une réduction des ressources par une réduction des modèles. Une technique d'optimisation émergeante est la distillation de modèles. Le principe est qu'un réseau, l'enseignant, distille ses connaissances dans un réseau plus léger, le réseau élève.

Deux verrous apparaissent.

- Le premier est que le modèle enseignant n'est pas déployable dans des ressources « legères ». Cette technique d'optimisation ne peut être déployée dans une infrastructure Edge uniquement.

- Le second est que la base de données doit être utilisée par les deux modèles, la confidentialité n'étant pas respectée comme l'est dans l'apprentissage fédéré.

L'objectif de la contribution est de proposer une méthode de distillation adaptée à des infrastructures de Edge Computing, dans lesquelles seules des ressources légères sont disponibles et avec une séparation des données pour les deux modèles pour répondre à la « privacy » des données.

GUILLOU Suzanne - Auteur presentateur - Univ. Grenoble Alpes, CEA, Leti, F-38000 Grenoble, FRANCE, Grenoble, France - G2Elab, 38031 Grenoble CEDEX 1, FRANCE, Grenoble, France

LANNELUC Charley, VAUCHE Laura - Univ. Grenoble Alpes, CEA, Leti, F-38000 Grenoble, FRANCE, Grenoble, France, CREBIER Jean-Christophe - G2Elab, 21 rue des martyrs, CS 90624, 38031 Grenoble CEDEX 1, FRANCE, Grenoble, France

## 14.METHODOLOGIE POUR MESURER LA PLUS-VALUE ENVIRONNEMENTALE DES CONVERTISSEURS DE PUISSANCE A COMPOSANT GRAND GAP (SIC, GAN)

Comparée aux composants traditionnels silicium (Si), l'utilisation des WBG dans les convertisseurs permet de réduire les pertes énergétiques à l'usage. Cependant, l'électrification massive induit la multiplication des convertisseurs, contribue à l'augmentation de la consommation d'électricité, à la raréfaction des ressources et à l'accumulation des déchets d'équipements électriques et électroniques. Il est donc nécessaire de quantifier les impacts environnementaux des systèmes de conversion de puissance dans leur ensemble, dans leur contexte applicatif et sur tout leur cycle de vie. Ce constat amène les questions suivantes : Comment mesurer la plus-value environnementale des composants grands gap ? Quelles doivent être les conditions de durée de vie des composants grands gaps dans la perspective d'assurer la soutenabilité de l'électronique de puissance ?

La méthode proposée pour répondre à ces questions comprend 3 étapes principales :

- le dimensionnement de convertisseurs de puissance,

- le prototypage pour alimenter l'Inventaire de Cycle de Vie (ICV)

- l'Analyse de Cycle de Vie (ACV).

Le dimensionnement comprend le choix des dimensions et paramètres électriques des composants et la fréquence de fonctionnement. Les convertisseurs à base de WBG et à base de Si seront comparés à niveau de performance optimal, en minimisant les pertes, et cela toutes choses égales par ailleurs, grâce à un modèle basé sur les données constructeurs pour les composants actifs et passifs. L'unité fonctionnelle considérée pour cette étude est : Assurer l'alimentation électrique sans interruption d'un Datacenter avec une charge de 800W pendant 5 ans. Pour remplir cette unité fonctionnelle, le prototype réalisé est un convertisseur AC/DC PFC totem-pole permettant l'adaptation d'une source alternative AC 230V monophasé vers une charge continue 400V. Le prototypage permettra d'alimenter l'inventaire de l'ACV, mesurer les pertes, la température de fonctionnement, valider et affiner les modèles utilisés pour la conception du système et le calcul des pertes, valider les normes de compatibilité électromagnétique et s'assurer que les comparaisons sont pertinentes. Finalement, une fois l'ACV affinée grâce au prototype, une comparaison des impacts environnementaux pourra être effectuée, en fonction des applications choisies, faisant varier la durée de vie du transistor et donc la durée de vie du convertisseur.

CARON Grégoire - Auteur presentateur - IOUDITSKI Anatoli - Laboratoire Jean Kuntzmann, Saint-Martin-d'Hères, France, GUITARD Nicolas, CÉLI Didier - STMicroelectronics, Crolles, France

## 15.MODELE REDUIT LSTM POUR L'OPTIMISATION DE TRANSISTORS BIPOLAIRES A HETEROJONCTION SILICIUM-GERMANIUM

Pour améliorer les performances des transistors bipolaires à hétérojonction silicium-germanium et réduire leur consommation, on les miniaturise. Cela rend leur conception complexe et nécessite la fabrication de nombreux dispositifs sur plaquette de silicium processus long, coûteux en eau, électricité, produits chimiques - avant de converger vers un dispositif optimisé. Pour pallier partiellement ces inconvénients, on recourt à la conception par ordinateur (ou TCAD) pour simuler les caractéristiques électriques des transistors. Cependant, cela requiert de nombreux coûteux calculs numériques. Ici, nous présentons une technique basée sur l'utilisation d'un modèle mathématique « réduit », qui, une fois construit, remplace la TCAD.

Tout d'abord, on construit une base de données composée de couples « profils de dopage 1D de transistors ; caractéristiques électriques simulées par TCAD ». Pour limiter la taille de la base de données - et donc le nombre de simulations pour la générer - on se focalise sur des profils remplissant deux conditions. Premièrement, ils doivent être réalistes : pour cela, on utilise de l'échantillonnage de Monte-Carlo par rejet, accéléré par une méthode de classification binaire (SVM). Deuxièmement, ils doivent présenter un intérêt technologique : ici, on utilise de l'échantillonnage préférentiel itéré.

Ensuite, on utilise ces données pour entraîner un modèle « réduit » de réseaux de neurones récurrents, appelés LSTM (Long Short-Term Memory), pour prédire le plus précisément possible les caractéristiques électriques à partir de profils de dopage. On adopte une architecture dite « décodeur » et on montre qu'ils sont plus précis que des réseaux « denses » classiques.

Enfin, on utilise nos modèles pour chercher des profils optimisés, selon deux axes. Premièrement, on réalise de l'optimisation biobjectifs en générant le front de Pareto entre deux Figures de Mérite (fréquence de transition et résistance de base). Deuxièmement, on génère un profil optimisé qui répond à un cahier des charges donné, en parcourant rapidement l'espace de conception.

En conclusion, une fois installées, ces techniques permettent d'atteindre des objectifs ambitieux en termes de conception, en s'affranchissant des cycles de fabrication silicium et des simulations TCAD, utilisant ainsi le Machine Learning pour rendre plus durable la conception des transistors bipolaires.

Réf: A17113MP

PERALTA Maxime - Auteur presentateur - Univ. Grenoble Alpes, CEA, List, Grenoble, France

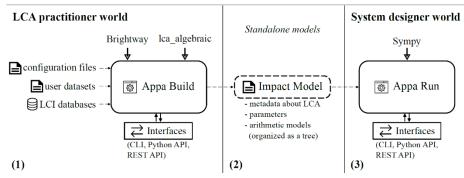

## 16.APPA LCA: UN WORKFLOW D'INTEGRATION DE L'ANALYSE DE CYCLE DE VIE POUR L'ECOCONCEPTION DES SYSTEMES NUMERIQUES

L'écoconception consiste à réduire les impacts environnementaux d'un produit ou d'un service sur l'ensemble de son cycle de vie, dès sa phase dans la conception. Ces impacts environnementaux peuvent être estimés en utilisant la méthode d'Analyse de Cycle de Vie (ACV).

Dans le domaine du numérique, deux facteurs freinent l'écoconception des systèmes et composants. Premièrement, réaliser l'ACV est une tâche complexe et chronophage, notamment à cause de la rareté des bases de données d'impacts numériques et de leur couplage fort avec un logiciel d'ACV spécifique et souvent propriétaire. Deuxièmement, il est compliqué de coupler directement un logiciel d'ACV avec un environnement de conception de par le manque d'interface de programmation, et à cause des compétences différentes demandées pour l'ACV et la conception numérique.

Nous proposons le workflow Appa LCA (Automatable, Portable and Parametric Life Cycle Assessment) qui résout ces deux problèmes. Appa LCA consiste à découper le logiciel d'ACV en deux parties indépendantes

Un logiciel à destination de l'ingénieur ACViste lui offrant des fonctionnalités simplifiant l'ACV de systèmes numériques, tel que l'import de données de différentes bases de données, ou des fonctions avancées de paramétrage, et permettant d'exporter des modèles d'impacts paramétriques et modulaires. Ces modèles d'impacts peuvent s'exécuter en standalone, c'est à dire sans avoir besoin du logiciel ou de bases de données d'ACV.

Un logiciel destiné à l'ingénieur en charge de la conception du système. Ce logiciel est léger et s'interface facilement avec n'importe quel logiciel, ou flot de conception, et permet d'exécuter les modèles d'impacts. L'ingénieur système peut donc facilement calculer les impacts environnementaux du système étudié selon les paramètres de conception, en toute autonomie.

Nous avons proposé une implémentation Python de ces deux composants et l'avons partagé en open source.

Nous développons une preuve de concept de l'utilisation d'Appa LCA dans un environnement de conception numérique en l'intégrant sous forme de plugin dans la plateforme de conception d'IA embarqué open source Aidge.

Nous avons réalisé un modèle d'impact d'accélérateur IA embarqué, et nous avons développé une interface utilisateur et obtenu des premiers résultats d'impacts environnementaux en fonction de différentes options de conception.

FIGURE: Workflow d'Appa LCA, séparant le logiciel ACV en deux outils indépendants.

LE GARGASSON Pierre - Auteur presentateur, PELCAT Maxime, BEUVE Nicolas, PRESSIGOUT Muriel, MORIN Luce, Ménard Daniel Univ. Rennes, INSA Rennes, France

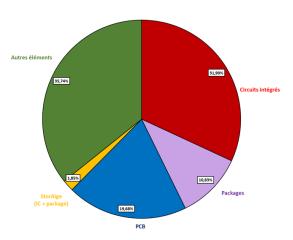

### 17.ÉTUDE ET MODELISATION DE L'IMPACT CARBONE DES CIRCUITS IMPRIMES

Un circuit imprimé (PCB) constitue un élément essentiel des cartes électroniques. Il s'agit de la plaque, généralement verte, assurant le support mécanique et les connexions électriques des composants électroniques. Il s'agit d'un assemblage de différentes couches électriques ou isolantes, tel un mille-feuille. La fabrication des PCB fait appel à de nombreux processus mécaniques et thermiques, par exemple, le pressage à haute température et pression, ou le perçage. La fabrication des PCB requiert également l'usage d'une grande variété de produits chimiques, par exemple, le développement d'une couche photosensible ou la gravure en bain d'acide.

Le vaste déploiement des systèmes électronique dans nos vies courantes représente une quantité phénoménale de matières premières et d'énergie de transformation. À titre d'exemple en 2021, la production mondiale de PCB s'est élevée à 464,1 M m2 pour un chiffre d'affaires de 80 449 M\$ US[i]. Bien que l'impact environnemental des composants électroniques soit plus élevé que celui des PCB, il est toutefois nécessaire d'étudier l'impact environnemental de ces derniers. Une première action consiste le mesurer grâce à l'analyse du cycle de vie (ACV), une méthode où l'analyste modélise les processus de fabrication du produit étudié. Le choix des étapes chronologiques est libre et dans notre cas, nous étudions les impacts environnementaux sur un périmètre « cradle-to-gate », depuis la mine jusqu'au quai d'expédition de l'usine de fabrication du produit étudié. Les étapes d'usage et de fin de vie ne sont pas considérées du fait de leur grande variété.

L'ACV se base sur un inventaire. Ceux proposés actuellement sont partiels. Un PCB possède en effet une multitude de critères de fabrication, tels que le nombre de couches électriques, le type de vias, le type de finitions, etc... Ces critères influencent les quantités de matière et d'énergie saisies dans l'inventaire. Après avoir abordé la fabrication d'un PCB, nous présentons sa modélisation et les difficultés rencontrées en vue de constituer l'inventaire d'ACV. Nous présentons les études existantes, la confiance que nous pouvons accorder à leurs résultats, ainsi que l'étude d'un modèle d'émission de gaz à effet de serre.

[i] https://www.prismark.com/pcb-sample-report

Réf: A17095VJ

JOGUIN Vincent - Auteur presentateur - Eupalia, Hyères, France

### 18.GENERAL-PURPOSE LONG-LASTING COMPUTING PLATFORM

Olonys is a computing platform designed for both hardware and virtual implementations, and to expose the least possible adherence to external particular features. Its fundamental approach is to turn as much computing hardware complexity as possible into software, and to provide adaptive mechanisms to access peripheral devices. It is in line with the concept of permacomputing.

Olonys features a nested processor architecture, comprising 5 sub-processor layers of increasing complexity and efficiency, all with register-based Instruction Set Architectures, from a processor operating with only two instructions (namely "subtract with borrow" and "store"), up to a full-featured, extensible processor similar to the RISC-V or ARM processors. Implementation of the latter may rely on the implementation of any of the 5 layers, offering a variety of trade-offs. In particular, the ISAs of the three more complex layers are optimized for dynamic recompilation.

The basic Olonys layer (called Lin'OlonysURisc) is so simple that introducing a non-obvious bug in its implementation is next to impossible, which guarantees that the execution environment supporting the whole software stack is extremely robust to variations in the underlying environment, especially over extended periods of time when knowledge fades away, i.e., all software running within the Olonys environment will continue to work in exactly the same way over platforms and through time.

With the three simpler layers already fully specified and implemented, work is ongoing to complete the specification of the two more complex ones, and to evaluate which compiler and operating system would be most suitable for feature-rich user applications, with support from the EC through the LEVIATAD Eurocluster. One important aspect pursued for the top

Nested VM architecture

Digital content

Vers

URisc

URis

URisc

URI

layer is specification completeness, excluding any unspecified state that could cause software behavior differences across implementations.

A partial implementation of the Olonys technology was already integrated within a century-scale digital archiving solution on durable optical carriers (namely paper and film), and tested extensively since 2020 by Andra, the French national radioactive waste management agency. This solution, Micr'Olonys, includes a self-contained primer that bootstraps the Olonys environment to run software that decodes custom 2D barcodes containing user data, complete with error correction and decompression.

FIGURE: Olonys architecture overview

DEVILLAINE Louis- Auteur presentateur - Université Grenoble-Alpes, Grenoble, France - MIAI, Grenoble, France

# 19.LE NUMERIQUE DURABLE PEUT-IL ETRE ANTI-ECOLOGIQUE ? RECIT D'UNE MANIFESTATION CONTRE L'INDUSTRIE DE LA MICRO-ELECTRONIQUE GRENOBLOISE

La France investit massivement dans l'industrie de la micro-électronique. Lors de son discours à Crolles, il y a deux ans, le président Macron a annoncé un grand plan d'investissement de plusieurs milliards d'euros pour l'agrandissement de l'usine de production de composants électroniques. Cet investissement s'inscrit dans une stratégie double de ré-industrialisation du territoire national et de regain d'une souveraineté dans un marché stratégique, celui des semi-conducteurs (Macron, 2022). Les arguments portent également sur la nécessité de ces composants pour assurer la transition énergétique.

Pourtant, cette extension fait l'objet d'une contestation bruyante dans la région et des collectifs se sont constitués pour critiquer ces choix socio-économiques. Le débat porte, de façon centrale, sur la gestion des ressources en eau par l'industrie de la micro-électronique, qualifiée « d'accaparement » (« Eau : Des centaines de manifestants », 2023). Des chantiers de rénovation en effet été menés pour permettre à la localité d'avoir accès à l'eau dont elle a besoin (Le Clerre, 2024).

Cette controverse s'accompagne d'événements de contestation qui prennent la forme de manifestations publiques. En avril 2024, l'une de ces manifestations, intitulée « De l'eau, pas des puces », se tient à Grenoble, et compte environ 850 participants d'après les relevés officiels (Demenus, 2024). A cette occasion, nous nous sommes penchés, dans la lignée des travaux en sociologie des mobilisations (Favre et al., 1997), sur les motivations des manifestants (militants ou non) en cherchant à mieux comprendre les raisons de leur venue.

Notre enquête montre qu'au-delà des enjeux liés à l'eau, la contestation contre l'industrie de la micro-électronique fait état d'une grande diversité de motifs, comptant parmi eux la crainte pour les conséquences environnementales de l'extension de l'usine, un plaidoyer pour la décroissance, la volonté de s'engager dans une mobilisation collective. A travers la question de l'eau, c'est en réalité une critique plus large qui est adressée à la stratégie de ré-industrialisation.

Cette contribution en sociologie cherchera à éclairer les débats sur la soutenabilité du numérique en se déportant du point de vue strictement technique et en apportant une perspective sociale, ancrée dans le territoire local.

Réf: A17085IS

SERVIN Isabelle - Auteur presentateur - LOPES-BARBOSA Joao-Carlos, SARRAZIN Aurélien, GODAT Sébastien, BOUCHARD Julien, RIVOIRA Yannick, VAUCHE Laura, DI CIOCCIO Lea, PAIN Laurent, CEA-Leti, GRENOBLE, France

## 20. ANALYSE DE CYCLE DE VIE DE LA FABRICATION DE SEMICONDUCTEURS: UN GUIDE POUR LA REDUCTION DES IMPACTS ENVIRONNEMENTAUX

To limit global warming by 1.5°C target in the Paris Agreement, emissions need to be reduced by 45% by 2030 and reach net-zero by 2050. The semiconductor industry should also apply a decarbonization plan to reduce its greenhouse gases emissions, preserve energy, water and other resources. The Life Cycle Inventory (LCI) and Life Cycle Assessment (LCA) in this context, particularly in clean rooms, play a crucial role in helping to identify key areas of energy, resource consumption, waste generation and their main impacts; and consequently to define actions to mitigate the environmental footprint of semiconductor manufacturing.

The LCA methodology involves assessing the environmental aspects and potential impacts of a product, process, or system over its entire life cycle - from raw material extraction, production, use, and disposal. Life Cycle Inventory (LCI) include metrics such as energy use, resource consumption (e.g., water, chemicals, metals), air emissions (e.g., CO?, PFCs), and waste generation towards water. Using Product Environmental Footprint (PEF) method, recommended by the European Commission [1], we have evaluated the environmental impacts of the fabrication of integrated circuits (IC) on 200 & 300 mm diameter Silicon wafers, which involves assessing both the impact of infrastructure to maintain ultra?clean environments (clean rooms) and of the process steps [2-5].

The LCA we have carried out show that the main environmental impacts come from the energy use; the use of fluorinated compounds (FCs) with a high global warming potential (GWP) in etching process and their waste management; the use of metals with high environmental impacts such as Au, and the use of hazardous chemicals in processes such as photolithography and wet steps. We will illustrate eco-design solutions such as substituting conventional chemistries with water-based materials or non-toxic chemistries, replacing high GWP gas with low GWP gas, or reducing energy and water consumption.

- [1] PEF Product Environmental Footprint Category Rules Guide, 2018.

- [2] Lopes Barbosa J. et al. "Development of a methodology to build a database for life cycle inventories in a semiconductor research centre" J. Clean. Prod., accepted (2024)

- [3] Servin I. et al. "Chitosan as a water-based photoresist for DUV lithography" Proc. SPIE 12498 (2023)

- [4] Renaud M, et al. "Life Cycle Assessment of etching processes for FDSOI transistors technologies" Proc. SPIE 12958 (2024)

- [5] Vauche L. et al. "Cradle to Gate Life-Cycle Assessment (LCA) of GaN Power Semiconductor Device", Sustainability, 15, (2023)

Réf: A17084JC

CREBIER Jean-Christophe - Auteur presentateur - CNRS/G2ELab, GRENOBLE, France

### 21. BEYOND THE QUEST FOR PERFORMANCE IN CONVERSION ELECTRONICS

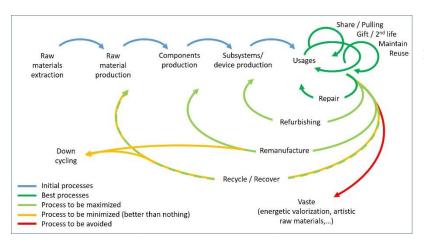

The quest for performance has long been a useful "driver" and source of progress and innovation in power electronics (PE). Current power densities and efficiencies, close to absolute limits, now leave little room for improvement of this very mature technology. However, the energy transition, which leads to maximizing the use of the electricity vector at all levels of society, generates increasing environmental impacts affecting planetary limits. The development of an industrial sector and a conversion technology compatible with the circular economy is a main sustainability perspective. In our decision-making processes, design, technological choices and production and use conditions, it is urgent to question preferences and objectives to commit the sector to a sustainable future.

Looking at the deployment of the circular economy, or even the "functional economy", power electronics, just like the electronic cards of most products, is most often a sub-system and not an entire object/product. Consequently, the development of circularity in EP is to be considered and built as one of the sub-assemblies of the product, as can be the case of a traction chain inverter for an electric vehicle. Its rate of integration into the system is then fundamental. Circularity in EP is therefore, above all, conditioned by the "accessibility" of the converter as such (disassembly, collection and diagnosis). Then secondly, it is conditioned by the way in which the converter is designed with regard to one or more of the following scenarios: repair, reconditioning, direct reuse at the end of use or even recycling.

At G2Elab, with our academic and industrial partners, we develop design and more easy to assemble solutions in power electronics to promote circularity. Our main areas of research concern ecodesign tools and methods, design and production for disassembly, repair and reconditioning, diagnosis and decision support. Among our most important contributions, we study the benefits of modularity and standardization, and the impact of heterogeneities present at multiple levels in the converter. We will present an overview of our ongoing activities and collaborations during the workshop.

FIGURE: From linear economy to circularity

Réf: A17080OW

WEPPE Olivier - Auteur presentateur, CHOSSAT Jérôme, MARTY Thibaut, PRÉVOTET Jean-Christophe, PELCAT Maxime INSA Rennes, France

### 22. MODELES D'IMPACT CARBONE DES CAPTEURS D'IMAGE CMOS

Compte tenu des préoccupations croissantes concernant le réchauffement climatique, l'impact environnemental des dispositifs électroniques doit être scruté de près. Les analyses du cycle de vie (ACV) révèlent que les circuits intégrés (CI) sont les principaux contributeurs aux émissions de gaz à effet de serre dans ces dispositifs. Cependant, réaliser un inventaire pour déterminer l'impact des CI est une tâche complexe en raison du manque de données, et des études existantes sur les CI qui négligent souvent les capteurs d'image CMOS (CIS).

Malgré l'augmentation de l'utilisation des CIS, en particulier dans les smartphones, il manque des modèles complets pour évaluer leur impact environnemental. Cet article propose un ensemble de modèles multi-niveaux qui tirent parti des informations disponibles tout en prenant en compte les spécificités des CIS. Le modèle le plus complet intègre des facteurs tels que la surface totale de silicium, la localisation géographique (qui influence le mix énergétique) et le noeud technologique. Pour répondre à des scénarios où les données sont incomplètes, des modèles approchés sont conçus pour utiliser efficacement des paramètres moyennés.

Les modèles proposés sont appliqués à des capteurs fabriqués par STMicroelectronics et Sony, et ces résultats sont comparés aux résultats d'ACV existants du Fairphone 4. Notre approche offre une compréhension plus globale de l'impact environnemental des CIS, contribuant ainsi à l'objectif plus large de réduction de l'empreinte carbone des dispositifs électroniques. Nos résultats suggèrent que l'impact carbone du capteur d'image du Fairphone 4 est probablement plus élevé que précédemment estimé, avec un écart significatif entre nos modèles et la valeur rapportée.

Figure: Les multiples capteurs d'image d'un Iphone

Réf: A17079PF

Pietro FERREIRA - Auteur presentateur, GRENNERAT Vincent, BERRO Rim, NGUYEN Nhu-Huan, VUONG Tan-Phu, XAVIER Pascal

Univ. Grenoble Alpes, Grenoble INP, Univ. Savoie Mont Blanc, Grenoble, France

### 23. SUSTAINABLE ELECTRONICS: WHAT KIND OF SUSTAINABILITY? SOME EXAMPLES IN THE FIELD OF MICROWAVE DEVICES

Society urges solutions for global warming and non-renewable resource depletion, while technology was the ultimate solution to any society crisis in the past century. Green technology (GreenTech) may the next industrial revolution shaping a new society aware of the environment limitations [1]. Since 2005, governments have introduced new regulations in terms of sustainability and issued few eco-labels in the technology market. Nowadays, consumers are aware of electronics' impact on environmental degradation and often look for reparable and energy-efficient technologies. Still, low environmental impact has become a major issue to develop GreenTech.

The Centre for Radiofrequencies, Optic, and Microelectronics in the Alps (CROMA) upholds a new research strategy to develop sustainable microwave electronics. Focusing on the efforts that could reduce most of the environmental footprint of electronic devices and contribute to a strong sustainability, microwave electronics must consider sustainable materials and manufacturing processes. Besides, devices must focus on low energy solutions, limiting carbon emissions during their lifecycle. Moreover, technology maintenance and recycling shall gain increased significance to extend devices lifetime and to reduce the environmental impact on electronics end-of-life stage. This paper summarizes recent scientific contributions in GreenTech to achieve both compact and conformable connected devices using a multiphysical approach.

First, Eco-design of devices by additive printing, low impact flexible or rigid substrates are of growing importance, where CROMA and his partners have obtained encouraging results. Through ANR and EIC funding, we tackle these challenges in materials characterization and design optimization of electronic boards and antennas [2-5]. By bringing AI to the sensor edge through edge-AI, it becomes possible to give IoT more flexibility in energy management and decision-making. CROMA research efforts are already aimed in diversifying such solutions towards neuromorphic sensors and energy efficiency, as well as their applications in harsh environments [6-8]. Finally, maintainability and recycling of devices must be done with a holistic transdisciplinary approach. CROMA promotes through the creation next January of the GdR called "DEFIE" (for "Devices in Electronics with Flat Impacts on the Environment") to gather more than 140 researchers all around the French territory closing the loop with economic and ecological efficiency [9,10].

[1] 10.1109/AGEC.2005.1452308

[2]10.1002/mop.32233

[3]10.1109/EPTC56328.2022.10013255 [4]10.23919/EuMC54642.2022.9924459

[5] 10.1109/LAEDC54796.2022.9908189

[6] 10.1109/ACCESS.2023.327543

[7] 10.1007/s10470-023-02164-w

[8] 10.29292/jics.v18i1.663

[9]10.1088/1361-6528/ad66d3

[10] 10.1016/j.susmat.2024.e00902

GRENNERAT Vincent - Auteur presentateur, XAVIER Pascal, JEANNIN Pierre-Oliver Grenoble-INP, Grenoble, France

# 24.ÉCO-CONCEPTION DU PCB : COMMENT AMELIORER SON CYCLE DE VIE GRACE A DES BIO-MATERIAUX ET DE NOUVELLES APPROCHES DE CONCEPTION DE LA CARTE ELECTRONIQUE

La réduction des déchets ultimes d'équipement électriques et électroniques (DEEE) passe aussi par la réduction de la part liée au circuit imprimé (PCB). Les analyses de cycle de vie des produits électroniques placent la part du PCB entre 5 et 25 % des impacts écologiques de la carte électronique. En effet, il concentre une part importante des métaux dans les brasures et dans les couches conductrices de cuivre. La part de cuivre qui y est stockée pendant toute la durée de vie du produit est significative. De plus, il est mal collecté et faiblement recyclé en fin de vie. Revisiter nos techniques de conception de la carte électronique en vue de réduire la quantité de cuivre dans la carte, tout en conservant sa pleine fonctionnalité, sa fiabilité et sa durabilité nous semble pertinent.

Par ailleurs, les composites utilisés dans les PCB types FR4 (principalement de la résine époxy et des fibres de verres) ne sont pas recyclables et les retardateurs de flamme actuellement utilisés sont très impactants pour l'environnement, alors que des alternatives biosourcées deviennent crédibles. Pour une transition rapide, il est important que celles-ci soient compatibles avec l'outillage industriel de fabrication soustractive actuel, ainsi qu'avec les techniques classiques d'assemblage de la carte électronique.

Nos réalisations et caractérisations de premiers démonstrateurs de complexité significative (carte micro-contrôleur, carte FPGA) ainsi que ceux en cours d'étude (micro-onduleur) ouvrent la voie de ces nouveaux substrats et mettent en lumière les verrous restant à lever.

En fin de vie de la carte électronique, les principaux métaux présents sur le PCB et sur les composants non démontés peuvent être récupérés de manière sélective par le procédé écologique de bio-hydrométallurgie (ou bio-lixiviation) et éviter le faible rendement de la pyro-métallurgie, actuellement utilisée uniquement sur les cartes à forte valeur ajoutée. Nos premiers résultats montrent l'importance du contrôle de la concentration des métaux et de la sélection des consortiums de bactéries utilisés en bio-lixiviation. Cette étude montre qu'une part de l'efficacité du traitement de fin de vie du PCB réside aussi dans les choix faits lors de l'étape de conception de la carte électronique.

Réf: A16959JA

ATTANE Jean-Philippe - Auteur presentateur - NELLOW, Grenoble, France - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, SGARRO Paolo - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, KANDAZOGLOU Aurélie - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, TERESI Salvatore - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, FROTTIER Théo - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France , GIANNONE Vincenzo - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, GIANNONE Vincenzo - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, SAVERO TORRES Williams - NELLOW, Grenoble, France, OSANA Filip - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, HUTIN Louis - CEA, LETI, GRENOBLE, France, NOÉ Pierre - CEA, LETI, GRENOBLE, France , LAGRAVE Jules CEA, LETI, GRENOBLE, France, HIPPERT Françoise - LMGP, Université Grenoble Alpes, Grenoble INP, CNRS, Grenoble, France, DORY Jean-Baptiste - CEA, LETI, GRENOBLE, France, PRENAT Guillaume - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, VILA Laurent - NELLOW, Grenoble, France - ,2 - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France, France, VILA Laurent - NELLOW, Grenoble, France - ,2 - Spintec (Université Grenoble Alpes / CEA / CNRS), Grenoble, France.

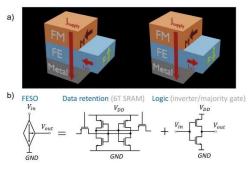

## 25.FERROELECTRIC SPIN-ORBIT DEVICES FOR ULTRALOW-POWER COMPUTING AND AI

This contribution presents a new spintronic/ferroelectric device, the FerroElectric Spin-Orbit (FESO) device, which allows for the direct and remanent control of spin-to-charge conversion through ferroelectric polarization. This conversion via spin-orbit coupling is demonstrated in two material types: Two-Dimensional Electron Gases (2DEGs) at oxide surfaces or interfaces and ferroelectric Rashba semiconductors. The FESO device signifies a major breakthrough in spintronics by offering the potential to reduce power consumption to the attojoule range while maintaining low operating voltages.

Spintronics has traditionally relied on ferromagnetic materials for spin generation and detection. However, recent interest has shifted toward non-magnetic systems due to the efficient spin-charge interconversion enabled by spin-orbit coupling. The FESO device, similar to the Magneto Electric Spin Orbit (MESO) device proposed by Intel [1], improves on previous designs by merging the writing and reading functions through ferroelectric control. This integration eliminates the need to switch magnetic states, enhancing performance in terms of non-volatility, magnetic field immunity, and energy efficiency. Additionally, it avoids the destructive reading process of Fe-RAMs and issues related to Magnetic Tunnel Junctions (MTJs).

We demonstrated the functionality of the FESO device in two classes of materials. First, in 2DEGs formed at oxide interfaces such as SrTiO? [2], applying an electric field induces ferroelectricity, enabling control over spin-to-charge conversion [3]. The process is characterized by hysteresis, with remanent states enabling non-volatile operation. Additionally, the spin-to-charge conversion efficiency in these materials is extremely high, surpassing that of heavy metals like W or Pt. Second, in ferroelectric Rashba semiconductors such as GeTe, the ferroelectric polarization reverses the Rashba spin-orbit coupling, altering the conversion sign at room temperature [4].

The FESO device presents a novel approach to spintronics, offering ultralow-power, non-volatile devices with high spin-charge conversion efficiency and enhanced logic density. Both material classes offer specific advantages and challenges for industrial use but could serve as the foundation for future energy-efficient computing platforms.

FIGURE: a) Operation of a ferroelectric-semiconductor-based FESO device. Depending on the ferroelectric polarization state of the ferroelectric semiconductor, the output current JSO produced within the Spin-Orbit (SO) material changes sign. b) Beyond non-volatili

- [1] S. Manipatruni et al., Nature 565, 35-42 (2019).

- [2] Gallego et al., Advanced Functional Materials, 34(3), 2307474 (2024).

- [3] P. Noel et al., Nature 580, 483-86 (2020).

- [4] S. Varotto et al., Nature Electronics 4, 740-747 (2021).

CHARLES Henri-Pierre - Auteur presentateur - CEA-List, Grenoble, France

## 26. Analyse de cycle de vie adapte au logiciel : outillages et recommandations

L'obsolescence du matériel arrive par l'évolution du logiciel plus que par le matériel. Les ordinateurs, téléphones portables sont changés parce qu'ils n'arrivent plus à exécuter correctement les applications du moment.

Dans cette présentation, nous mettrons à jour les mécanismes à l'oeuvre dans l'évolution des logiciels : l'économie invisible des outils logiciels, la chaîne de la valeur des logiciels, l'économie des entreprises de logiciel, l'évolution technique et sécuritaire des logiciels.

Plus précisément, nous montrerons les manques existant dans les chaînes de création de logiciels sur plusieurs exemples, illustrés par des expérimentations préliminaires.

Nous conclurons l'exposé par une liste de recommandations sûr, d'une part les manques d'outils techniques permettant de mesurer l'évolution des logiciels et d'autre par sur les aspects légaux qui pourraient être mis en oeuvre pour contrôler l'évolution des logiciels.

Réf: A17808RT

TATJE Romain - Auteur presentateur - Grenoble IAE, Saint-Martin-D'Hères, France, LE MOING Béatrice, ROUSSEL Valentin, GANA Sarah, SIBARI Myriam, ZOU Stella, MAKINADJIAN Lisa, EYMERY Christelle, PONCON Clara PONCON, VECCHINI Juliette – Schneider Electric

### 27. THE REALITY OF DIGITAL

The Reality of Digital est un projet collaboratif initié en 2024 entre Grenoble IAE et Schneider Electric. Ce projet avait pour but de sensibiliser les employés de Schneider Electric aux enjeux environnementaux, via une exposition artistique. Après six mois de travail, un groupe de six étudiants de Grenoble IAE a proposé une série de posters illustrant le cycle de vie des appareils électroniques, projet qui a été installé en septembre 2024 sur le site Intencity de Schneider Electric.

L'exposition se compose de six affiches, chacune abordant une phase du cycle de vie des objets électroniques : extraction des matières premières, production, utilisation, impacts sociétaux, recyclage, et effets des technologies digitales. Chaque affiche inclut un QR code menant à des informations complémentaires sur les impacts environnementaux et économiques. Depuis sa mise en place, l'exposition a attiré de nombreux visiteurs et généré un millier de vues en ligne.

Lors du symposium, l'équipe exposera le processus créatif et la méthodologie appliquée, en montrant comment cette initiative peut servir de modèle pour sensibiliser les employés d'autres entreprises.

Réf : A17807LM

HAUKLIEN Trond - Auteur presentateur, MONTES Laurent

Grenoble INP / UGA, GRENOBLE, France

## 28. AUTONOMOUS DUAL SENSOR USING GAN ON SILICON TECHNOLOGY FOR SUSTANAIBLE IOT

The global demand for wireless sensors is rising in our information-centric society. Used in IOT objects, buildings to monitor presence or energy consumption, or in vehicles to monitor longevity of motors or efficiency, sensors provide valuable data for decision-makers all over the world. With global warming becoming one of the biggest challenges for humanity to overcome, the transition to renewable energy sources and need for energy effective solutions is needed more than ever before. Real-time data from wireless sensors play a significant part of this shift towards green energy, but the implementation of such devices needs to be done in a sustainable way.

We present new device architectures based on GaN on SIlicon, autonomous dual sensors to provide wireless data collection without the need of a battery. The technology benefits from sustainable and non-toxic materials, in sensors that can be deployed remotely, without the need for maintenance. The dual sensor applies nanotechnology for vibrational energy harvesting. Combined with the material's photovoltaic properties, the aim is light- and vibrational energy so that the device can operate autonomously without batteries and send information packets wirelessly to a base station or master node.

Réf: A17806AE

ESCANDE Adrien - Auteur presentateur, CHECHAOUNI MOUSSAOUI Sélim, WIEBER Pierre-Brice

Inria, Grenoble, France

### 29. CONTRÔLE FRUGAL DE ROBOT

Le nombre de robots produits chaque année est encore faible en comparaison avec d'autres productions humaines, mais les projections prévoient une forte augmentation dans les décennies à venir, de paire avec une complexification (cela sans tenir compte des problèmes de matériaux critiques pouvant limiter ce développement). Il est donc important de s'attacher à diminuer l'empreinte de ces machines.

Une part conséquente de la consommation énergétique d'un robot vient des calculs nécessaires pour son contrôle. Une approche typique est de résoudre à chaque cycle de contrôle un problème d'optimisation numérique pour décider de la prochaine commande à exécuter. Les calculs sous-jacents se font à la précision maximale permise par le hardware, sans se poser la question de la pertinence de cette précision. Ils se basent cependant sur des données capteur assez peu précises et sur des modèles du robot et de l'environnement qui ne sont pas parfaits. De même, le robot n'est pas capable d'exécuter exactement la commande qu'il reçoit. Les hypothèses de ce travail sont qu'on peut atteindre la même précision de mouvement pour un robot en effectuant des calculs moins précis, et que cela permet de faire moins de calculs, ouvrant la porte à des économies d'énergie. Être capable de gérer l'inexactitude des calculs donne aussi la possibilité de contrôler des robots faits de matériaux ou capteurs plus durables et souvent moins précis.

Nous vérifions ces hypothèses dans le cadre d'un contrôleur de l'état de l'art, basé sur la résolution d'un problème d'optimisation quadratique (QP), appliqué à un bras robotique ou à un robot humanoïde, pour une tâche de suivi de trajectoire. Nous étudions d'abord la relation entre la qualité du contrôle et la précision des calculs, modélisée par un bruit rajouté au contrôleur. Nous montrons ensuite qu'on peut baisser la fréquence de certains calculs faits dans le QP, et donc baisser la précision du contrôleur, sans baisse mesurable de la qualité du contrôle. Cela permet de réduire par environ 25 le temps de calcul dédié au contrôle. Cette approche de contrôle frugal est générale et semble pouvoir s'étendre à d'autres types de robot ou de contrôleur.

Réf: A17805GD

DEPRES Gael - Auteur presentateur, THENOT Victor, JOYARD-PITIOT Blandine, SEIGNARD Juliette FEDRIGONI, VOIRON, France

## 30. Fabrication d'une electronique ecoresponsable en utilisant du papier et des procedes l'electronique imprimee

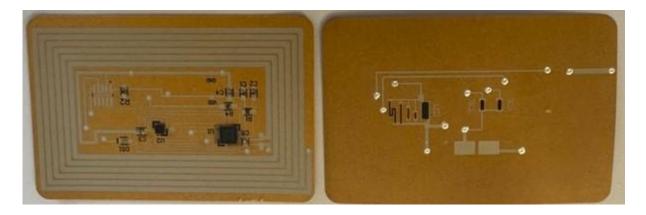

Les emballages, les étiquettes intelligentes mais aussi les Printed Circuit Board (PCB) représentent un énorme marché potentiel. Avec la volonté de minimiser l'impact sur l'environnement et de s'inscrire dans une économie circulaire, l'objectif de ce travail est de montrer pourquoi l'électronique imprimée sur papier est une alternative par rapport aux approches conventionnelles. L'électronique imprimée sur papier est aujourd'hui une réalité et les lignes d'impression pour fabriquer des étiquettes et des emballages intelligents ont atteint, chez FEDRIGONI, l'échelle industrielle. Différents objets - tags NFC et UHF, détection d'ouverture, capteurs de température... - qui peuvent être imprimés industriellement seront détaillés.

Le programme de recherche et développement de FEDRIGONI sera présenté, y compris les capteurs (température, humidité, chocs, pH...), les écrans électrochromiques imprimés, les batteries imprimées et d'autres systèmes.

La recyclabilité de ces dispositifs imprimés sur papier est également à souligner. Les résultats seront présentés et analysés pour 3 exemples : une étiquette en papier à détection de chocs, une étiquette en papier anti-contrefaçon. Une étude d'analyse du cycle de vie (ACV) sera également présentée pour une carte papier à puce.

Enfin, nous détaillerons un projet collaboratif "CircEl-Paper" sur le remplacement des PCB verre/époxy par des PCB à base de papier et de résine biosourcées. Ces nouveaux PCB sont fabriqués à partir de papiers traités pour être ignifuges, résistants aux bains chimiques et très stable dimensionnellement. Ils permettent donc l'électrodéposition ainsi que la fabrication de multicouches avec des via conducteurs pour fabriquer des systèmes complexes.

PCB Papier hybryde recto/verso

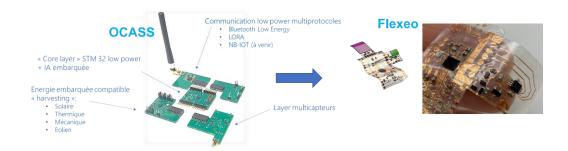

Réf: A17802sb